Mô tả sản phẩm

A3P250-PQG208I IC logic lập trình FPGA Mảng cổng lập trình trường FPGA A3P250-PQG208I LEAD MIỄN PHÍ

Các tính năng và lợi ích

Công suất cao

• Cổng hệ thống 15 K đến 1 M

• Lên đến 144 Kbits của SRAM hai cổng thực

• Công nghệ Flash có thể lập trình lại I / Os lên đến 300 người dùng

• 130 nm, 7 lớp kim loại (6 đồng), Quy trình CMOS dựa trên Flash

• Hỗ trợ tức thì ở mức 0

• Giải pháp một chip

• Giữ lại Thiết kế được Lập trình khi Cung cấp Hiệu suất Cao

• Hiệu suất hệ thống 350 MHz

• 3.3 V, 66 MHz 64-Bit PCI † Lập trình trong hệ thống (ISP) và Bảo mật

• ISP sử dụng giải mã tiêu chuẩn mã hóa nâng cao 128-bit trên chip (AES) (ngoại trừ thiết bị ProASIC®3 hỗ trợ ARM®) qua JTAG (tuân thủ IEEE 1532) † • FlashLock® để bảo mật FPGA có nội dung nguồn điện thấp

• Điện áp lõi cho nguồn điện thấp

• Hỗ trợ hệ thống 1.5 V-Only

• Bộ chuyển mạch Flash trở kháng thấp Hệ thống phân cấp định tuyến hiệu suất cao

• Cấu trúc đồng hồ và định tuyến theo phân đoạn, phân cấp

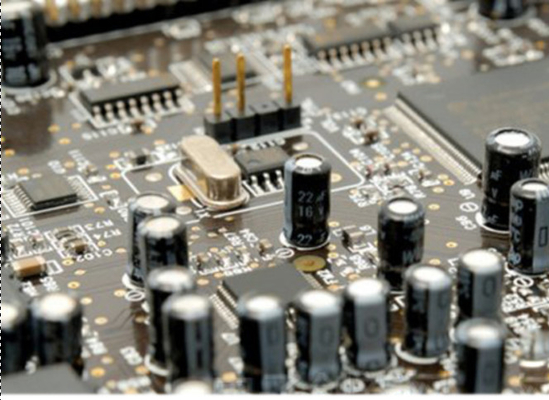

I / O nâng cao

• 700 Mbps DDR, LVDS-Capable I / Os (A3P250 trở lên)

• Hoạt động điện áp hỗn hợp 1,5 V, 1,8 V, 2,5 V và 3,3 V

• Hỗ trợ điện áp nguồn cung cấp phạm vi rộng trên mỗi JESD8-B, cho phép I / Os hoạt động từ 2,7 V đến 3,6 V

• Điện áp I / O có thể lựa chọn của ngân hàng — tối đa 4 ngân hàng trên mỗi chip

• Tiêu chuẩn I / O một đầu: LVTTL, LVCMOS 3.3 V / 2.5 V / 1.8 V / 1.5 V, 3.3 V PCI / 3.3 V PCI-X † và LVCMOS 2.5 V / 5.0 V Đầu vào

• Các tiêu chuẩn I / O khác nhau: LVPECL, LVDS, B-LVDS và M-LVDS (A3P250 trở lên) • Các thanh ghi I / O trên các đường vào, ra và kích hoạt • I / Os có thể thay đổi nóng và lạnh ‡

• Tốc độ quay đầu ra có thể lập trình † và cường độ truyền động

• Kéo lên / xuống yếu

• Kiểm tra quét ranh giới IEEE 1149.1 (JTAG)

• Các Gói Tương thích Pin trên Mạch Điều hòa Đồng hồ Gia đình ProASIC3 (CCC) và PLL †

• Sáu khối CCC, một khối có PLL tích hợp

• Dịch chuyển pha, nhân / chia, khả năng trì hoãn và phản hồi bên ngoài có thể định cấu hình

• Dải tần số đầu vào rộng (1,5 MHz đến 350 MHz) Bộ nhớ nhúng †

• 1 Kbit bộ nhớ không linh hoạt của người dùng FlashROM

• SRAM và FIFO với khối RAM có thể thay đổi tỷ lệ khung hình 4.608-bit (các tổ chức × 1, × 2, × 4, × 9 và × 18) †

• Hỗ trợ bộ xử lý ARM hai cổng thật SRAM (ngoại trừ × 18) trong ProASIC3 FPGA

• Thiết bị M1 ProASIC3 — Bộ xử lý mềm ARM®Cortex®-M1 Khả dụng có hoặc không có Gỡ lỗi